BİL 361 – BİLGİSAYAR MİMARİSİ VE ORGANİZASYONU

2015-2016 Güz Dönemi

ÖDEV 4

Son Teslim Tarihi/Saati : 17.12.2015/23:59

Teslim Şekli: e-posta

Teslim Yeri : hhassan@etu.edu.tr

Uyarı: Bu ödevdeki soruları öğrenciler kişisel çabalarıyla cevaplamalıdır. Grup halinde

ödev hazırlanması, çözümlerin tamamen veya kısmi olarak dersi alan veya almayan

başka herhangi biri tarafından yapılması durumunda, bu öğrenciler ödevde kopya

çekmiş sayılacak ve gerekli işlemler yapılacaktır.

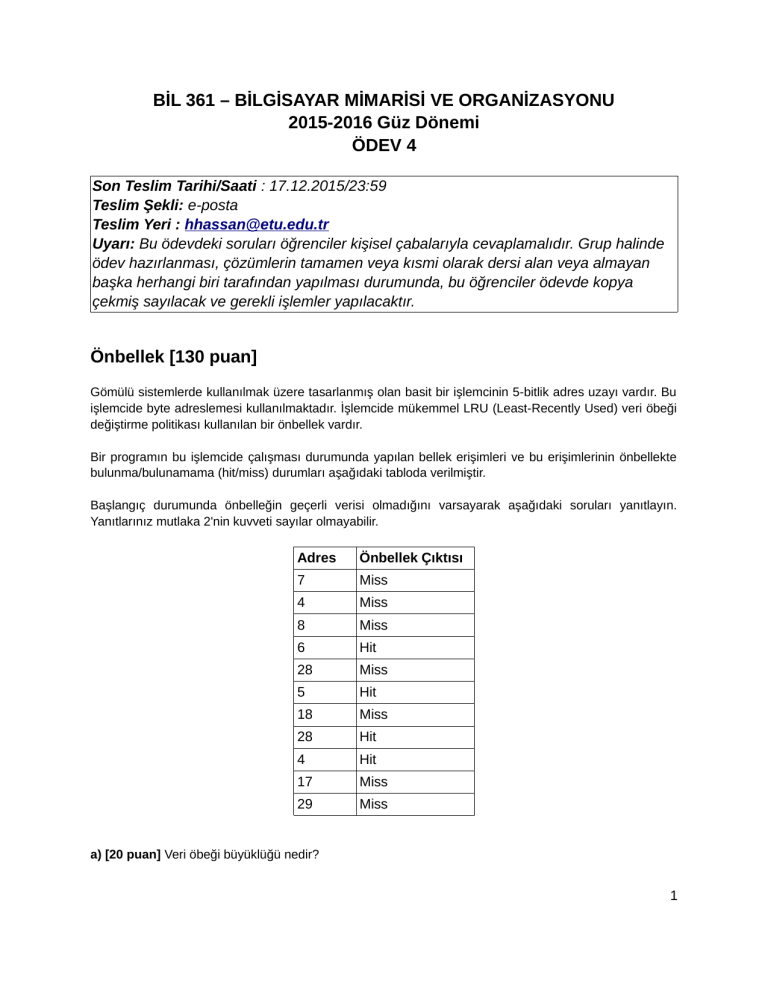

Önbellek [130 puan]

Gömülü sistemlerde kullanılmak üzere tasarlanmış olan basit bir işlemcinin 5-bitlik adres uzayı vardır. Bu

işlemcide byte adreslemesi kullanılmaktadır. İşlemcide mükemmel LRU (Least-Recently Used) veri öbeği

değiştirme politikası kullanılan bir önbellek vardır.

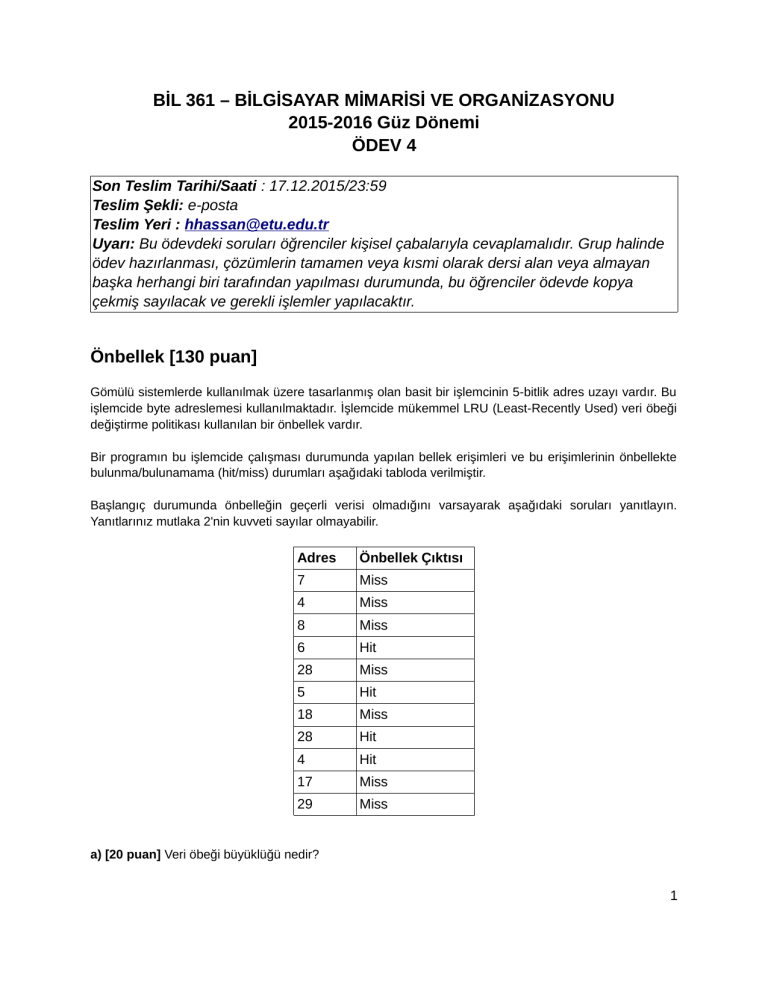

Bir programın bu işlemcide çalışması durumunda yapılan bellek erişimleri ve bu erişimlerinin önbellekte

bulunma/bulunamama (hit/miss) durumları aşağıdaki tabloda verilmiştir.

Başlangıç durumunda önbelleğin geçerli verisi olmadığını varsayarak aşağıdaki soruları yanıtlayın.

Yanıtlarınız mutlaka 2'nin kuvveti sayılar olmayabilir.

Adres

Önbellek Çıktısı

7

Miss

4

Miss

8

Miss

6

Hit

28

Miss

5

Hit

18

Miss

28

Hit

4

Hit

17

Miss

29

Miss

a) [20 puan] Veri öbeği büyüklüğü nedir?

1

b) [20 puan] Önbellek kaç yollu kümeli ilişkili yapıdadır?

c) [20 puan] Önbellekte kullanılan etiketler kaç bittir?

d) [20 puan] Önbelleğin veri saklama kapasitesi nedir?

e) [50 puan] Bu önbelleği Verilog kullanarak gerçekleyin. Önbellek modülünün giriş/çıkış arayüzü

aşağıdaki gibi olmalıdır. X ve Y olarak verilen giriş/çıkış sinyallerinin uygun bit genişliklerini önceki

şıklarda bulduğunuz veri öbeği büyüklüğü, önbellek kapasitesi, vs. değerlerine göre belirleyin. Önbellekte

istenilen adreste verinin bulunması 1 çevrimde tamamlanmaktadır. Diğer işlemlerin kaç çevrim süreceği

aşağıda anlatılmıştır. Önbelleği Write-back (işlemciden gelen isteği sadece önbelleğe yaz, veri öbeği

atılırken ana belleğe yaz) olarak tasarlayın.

“rst” saatin (“clk”) yükselen kenarında senkron olarak çalışan reset girişidir. “rst” mantık-1 değerini

aldığında, saaatin yükselen kenarında önbellek temizlenmeli, yani tüm saklanan verilen geçersiz duruma

getirilmelidir.

İşlemci Arayüzü

• “ready” çıkışı önbelleğin bir sonraki bellek isteğini almaya hazır olduğunu göstermelidir. Bir bellek

isteğinin bellekte bulunamaması durumunda (miss) ana belleğe (Main Memory) gidilir. Ana

belleğe gönderilen okuma isteklerinin kaç çevrimde sonuçlanacağı bilinmemektedir. Ana bellekten

okuma işleminin tamamlandığı “mem_data_in_valid” sinyali mantık-1 olduğunda anlaşılmaktadır.

Ana belleğe yazma istekleri ise bir çevrimde tamamlanmaktadır. Eğer önbellek, ana bellekten

okuma isteği yaparsa, “ready” sinyali ana bellekten istenen veri gelene kadar mantık-0 olur ve

yeni bellek isteği kabul edilmemiş olur.

• “en” girişi işlemciden bir bellek isteği geldiğini belirtir.

• “wr_en” girişi işlemciden gelen bellek isteğinin yazma isteği olduğunu gösterir.

• “address” girişi işlemciden gelen, hangi fiziksel bellek alanına erişilmek istendiğini gösteren

sinyaldir.

• “data_in” girişi işlemciden gelen ve önbelleğe yazılacak veriyi gösterir.

•

•

“data_out” istenilen adresteki verinin önbellekte bulunması durumunda işlemciye gönderilen

veridir.

“data_out_valid” işlemciye giden, “data_out” çıkışının geçerli olduğunu ve bellek isteğinin

tamamlandığı gösteren çıkıştır. Bu çıkış sadece okuma (read) istekleri için mantık-1 olabilir.

Yazma işlemlerinin tamamlandığını göstermek için ise sadece “ready” sinyali kullanılır.

Ana Bellek Arayüzü

• “mem_en” mantık-1 olduğunda ana belleğe istek yapıldığını gösterir.

• “mem_wr_en” mantık-1 olduğunda ana bellek isteğinin yazma işlemi olduğunu gösterir.

• “mem_addr” ana bellek isteği ile hangi adrese erişilmek istendiğini gösterir.

• “mem_data_write” ana belleğe yapılan yazma isteklerinde yazılacak olan veri bu sinyal ile

gönderilir.

• “mem_data_read” ana bellekten okunan veriyi ifade eder.

• “mem_data_in_valid” ana bellekten okunan verinin “mem_data_read” girişinde geçerli olduğunu

gösterir.

Not: Tasarımınızda verilerin geçerli olup olmadığını gösteren “valid” bitlerini kullanmayı unutmayın.

2

module BIL361Cache (

input clk,

input rst,

//CPU Interface

output ready,

input en,

input wr_en,

input[4:0] address,

input[7:0] data_in,

output[7:0] data_out,

output data_out_valid,

//Main memory Interface

output mem_en,

output mem_wr_en,

output[X:0] mem_addr,

output[Y:0] mem_data_write,

input[Y:0] mem_data_read,

input mem_data_in_valid

);

3