İSTANBUL ÜNİVERSİTESİ

ELEKTRİK – ELEKTRONİK MÜHENDİSLİĞİ

ELEKTRONİK DEVRELER-II

LABORATUVARI

DENEY-1

“İşlemsel Kuvvetlendirici”

1

DENEY-1

İŞLEMSEL KUVVETLENDİRİCİ

ÖN HAZIRLIK

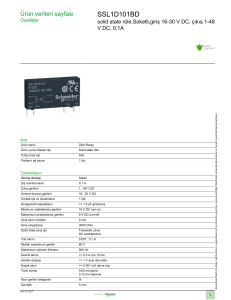

1. TL081 ve OP07C işlemsel kuvvetlendiricilerin kataloğunu inceleyerek aşağıdaki

parametrelerini kıyaslayınız, bacak bağlantılarını gösteren şemayı çizerek deneye getiriniz.

Maksimum besleme gerilimi, giriş kutuplama akımı, kayıklık (offset) gerilimi, sukunet

(quiscent) akımı, kazanç bant genişliği, giriş empedansı, değişim hızı vs.

2. Bir İK’ devresinde kazanç bant genişliği çarpımının (GBWP) sabit olması olgusunu

açıklayınız.

3. Ortak kip zayıflatma oranı (CMRR) nedir? Deneye gelmeden önce, verilen katalog

bilgilerinden bu büyüklüğün değerini bulunuz.

4. Her iki girişine aynı işaretin uygulandığı fark kuvvetlendiricisinin çıkış işaretinin ne olacağını,

CMRR ’i göz önüne alarak tartışınız.

5. Değişim hızı (Slew Rate) nedir? Deneye gelmeden önce kullanacağınız İK’ nin değişim hızını

bulunuz.

6. Bir kuvvetlendiricinin üst kesim frekansı ile girişine uygulanan ideal darbeye cevabının

yükselme zamanı arasındaki ilişki nedir?

7. Bir toplama ve eviren kuvvetlendirici kullanarak iki işaretin farkını alacak bir fark

kuvvetlendiricisi tasarlayınız.

8. (15) ifadesini çıkarınız.

9. Girişine aşağıdaki verilen işaret uygulanan entegratörün çıkışındaki işaretin zaman üzerinden

değişimini çiziniz. Bu işaret sabit bir A değeri olsaydı çıkış ne olurdu?

10. Kutuplama akımları ve kayıklık (offset) gerilimini bir entegratör devresinde etkisinin ne

olacağını tartışınız.

11. Tüm büyüklüklerin tanımın öğrendiğinizden emin olunuz.

12. A(t)=3.sin(200t) işaretinden B(t)=10 – 5.cos(200t) işaretini elde edilmesini sağlayan devreyi

işlemsel kuvvetlendiricilerle tasarlayınız.

2

İŞLEMSEL KUVVETLENDİRİCİ

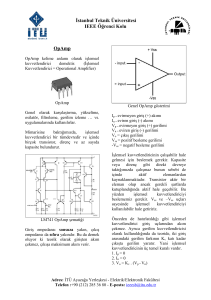

İşlemsel kuvvetlendirici (İK olarak kısaltılacaktır) alışılagelmiş kuvvetlendiricilerden farklı olarak, iki

girişi ve bir çıkışı olan elemanlardır. İK sembolü ve ilgili büyüklükler Şekil-1’de verilmişse de burada,

ileride de pek çok kere yapılacağı gibi, besleme gerilimleri gösterilmemiştir. “+” ile işaretlenmiş olan

ve Up giriş geriliminin uygulandığı girişi evirmeyen (faz döndürmeyen) ve Un geriliminin uygulandığı

“–“ ile işaretlenmiş girişi ise eviren (faz döndüren) giriş olarak isimlendirilir. Uo, İK’nın çıkışıdır. Bir

İK’nın içyapısı Şekil-2’de gösterildiği gibidir.

Rn, Rp girişlerle toprak arasındaki dirençleri; Cn, Cp ise

kapasiteleri göstermektedir. Rd ve Cd ise girişler arasındaki

direnç ve kapasitedir. Ro, kuvvetlendiricinin çıkış direnci, KOL

ise frekansa da bağlı olan açık çevrim kazancıdır. (OL: Open

Loop)

Aşağıdaki özelliklere sahip İK, “ideal

İK” olarak tanımlanır.

1. Rn, Rp, Rd

Cn, Cp, Cd

Ro

2. KoL>>1

Bu varsayımlarla;

.........(1)

eşitliği geçerlidir. Pek çok tümleşik İK, birçok uygulamada ideal varsayımlara yaklaşırlar.

Aşağıda İK’ları tanımlayan temel parametreler verilmiştir.

Açık Çevrim Kazancı (Open Loop Gain)

Daha önce tanımlanmış olan KOL, Şekil-3’te

gösterildiği gibi frekansa bağlıdır. İK’ nın alt

kesim frekansı 0 Hz’dir, dolayısıyla DC işaretleri

de kuvvetlendirir. KOL0 ile gösterilen alçak frekans

kazancı 106 mertebesindedir. f2 üst kesim frekansı

ise, sıradan İK’larda sadece birkaç Hz’dir. Bode

diyagramının f2’nin üzerinde eğimi 20 dB/dek’tir

ve genellikle f3 gibi ikinci bir kutbu daha vardır.

Bu kutbu göz önüne almadan, İK’ nin kazancı;

3

(2)

Küçük İşaret Birim Kazanç Bant Genişliği (Small Signal Unit Gain Bandwidth)

Kazancın 0 dB’e düştüğü frekanstır ve Şekil-3’te f c ile gösterilmiştir. Bode diyagramından görüldüğü

gibi

fc = KOL0.f2

(3)

Bağıntısı geçerlidir. (Dikkat: KOL0 dB cinsinden değil, oran olarak alınmalıdır). Bu büyüklük, kazanç

bant genişliği olarak da isimlendirilir.

Giriş Dengesizlik (Kayıklık) Gerilimi (Input Offset Voltage)

İK’ nın her iki girişi toprak potansiyeline bağlandığında Uid=0 olmasına rağmen çıkış gerilimi 0

olmayabilir. İK’nın giriş katında kullanılan transistör veya FET’lerin eş olmamasından kaynaklanan

bu hata, giriş dengesizlik gerilimi yardımıyla İK’nın analizine

katılabilir. Şekil-4’te gösterildiği gibi U0I giriş dengesizlik gerilimini

gösteren bir DC gerilim kaynağı İK’nın girişlerinden birine bağlanır.

UoI’nin yönü ve değeri, aynı tipten İK’larda bile elemandan elemana

farklılık gösterir.

Giriş Kutuplama Akımı (Input Bias Current):

Gerçek bir İK’da Rn, Rp ve Rd giriş dirençleri sonsuz büyük

olmadığından, çok küçük de olsa girişlerinden giriş kutuplama akımı

denilen

bir

akım

akar.

Şekil-5’te

gösterilen bu akımların değeri elemandan elemana ve ayrıca

sıcaklıkla değişir. FET girişli İK’larda bu akım, transistör girişlilere

göre daha azdır. Birçok uygulamada giriş kutuplama akımlarından

çok bunların farkı önemlidir ki bu fark giriş dengesizlik akımı (Input

Offset Current) olarak da bilinir.

Maksimum Çıkış Gerilimi (UOmax, UOmin)

Hem pozitif hem negatif gerilim kaynağından beslenen (ki buna simetrik besleme de denir) İK’larda

çıkış gerilimi hem pozitif hem de negatif değerler alabilir. Çıkış gerilimi her iki yönde de sınırlıdır ve

belli değerlerde doymaya girer. Klasik İK’larda besleme gerilimi ±15 V olup, çıkış geriliminin en

büyük değeri besleme geriliminin bir volt kadar altındadır.

Maksimum Güç Gerilimi

Girişlerden biri ile toprak arasına, İK tahrip olmaksızın uygulanabilecek en büyük gerilimi tanımlar.

Bu nedenle deneyde girişlere izin verilenden daha büyük bir gerilim uygulanmamasına özen

göstermelisiniz.

4

Maksimum Fark Giriş Gerilimi

İK ‘nın girişleri arasına İK tahrip olmaksızın uygulanmasına izin verilen en büyük gerilimdir.

Ortak Kip Giriş Gerilimi (Common Mode Input Voltage)

Her iki girişe uygulanan gerilimlerin ortalama değeridir. Bu gerilimi Ucm ile gösterirsek;

(4)

Genel olarak Un ve Up zıt fazda olduklarından Ucm=0’dır. İdeal bir İK sadece (Up-Un) farkını

kuvvetlendirirse de gerçek İK ‘ larda ortak kip giriş gerilimi de istenmeyen bir Uocm çıkış gerilimine

neden olur. İK ‘ların ortak kip giriş gerilimi ne derece bastırıldıkları (zayıflatıldıkları) kalitesinin bir

ölçütüdür. Bu ölçütü niceliksel olarak ifade edebilmek amacıyla ortak kip zayıflatma (bastırma) oranı

(CMRR: Common Mode Rejection Ratio) diye adlandırılan

(5)

ise çıkışta aynı Uocm

Parametreleri tanımlanmıştır ki, burada Ucm ortak kip giriş gerilimi,

gerilimini üretecek olan ve girişlerden birine uygulanan fark gerilimidir.(bakınız şekil-6)

CMRR çok büyük bir sayı olduğundan, hemen hemen her zaman bunun yerine

(6)

Uyarınca tanımlanmış olan dB cinsinden ortak kip zayıflatması kullanılır.

Değişim Hızı (Slew Rate, S)

Bir İK ‘nın girişine uygulanan işaret ne kadar hızlı değişirse değişsin, çıkış işaretinin değişim hızı

sınırlıdır. Bu olguyu, yüksek frekanslarda kazancın azalmasına bağlamak yanlış yorumdur. Zira

kazancın üst kesim frekansı, tr yükselme zamanı olmak üzere;

(7)

eşitliği uyarınca yükselme zamanını belirlerse de bu sadece küçük genlikli işaretler için geçerlidir.

Kuvvetlendiricinin içindeki kapasiteleri dolduran veya boşaltan akımların sınırlı olması, çıkış

geriliminin değişim hızını sınırlar. Bu büyüklük Şekil-7’de gösterildiği gibi tanımlanır.

5

Durulma Süresi (Settling Time, ts)

Girişine basamak fonksiyonu uygulanan İK’nın çıkış geriliminin son değerinin belli bir yüzdesine eş

genlikteki bir aralıkta kalıncaya kadar geçen süre olarak tanımlanır. (Bkz. Şekil-8). Dolayısıyla ts,

girişine bir basamak fonksiyonu uygulanan İK’da çıkışın son değerine, belirlenen hata sınırları içinde,

erişinceye kadar beklenilmesi gereken süredir.

İŞLEMSEL KUVVETLENDİRİCİLİ TEMEL DEVRELER

Eviren (Faz Döndüren) Kuvvetlendirici

Devre yanda verilmiştir. İ.K.’ nın ideal olduğu

varsayılırsa, giriş direnci sonsuz olduğundan

id=0 (İ.K giriş akımı=0) ve dolayısıyla ii=iF

olacaktır. Diğer taraftan

Ug = Ri.ii – Uid

(8)

Uid + RF.iF + Uo = 0

(9)

Çevre denklemleri, KOL→∞ (Açık çevrim

kazancı sonsuz) varsayımı ile Uo=KOL.Uid ve

Uid=Uo/KOL gerilimi sıfıra gideceğinden

(10)

(11)

Şekline dönüşür ki buradan kazanç

(12)

6

olarak bulunur. Eviren giriş ile toprak arasında çok büyük bir direnç olmasına rağmen, Uid

olması

nedeniyle, eviren giriş hemen hemen toprak (sıfır) potansiyelindedir. Bu olgu, eviren girişin görünürde

toprak potansiyelinde olduğu şeklinde ifade edilir. Kuvvetlendiricinin giriş direncinin Ri olduğunu da

siz gösteriniz.

(12) ifadesinden hareketle kazancı istediğimiz kadar büyük yapabileceğimizi düşünüyorsanız

yanılıyorsunuz. Bu ifade çıkarılırken KOL→∞ alınmış olduğunu hatırlayınız. Bu varsayımdan vazgeçip

(2) ifadesi ile verilen kazancı kullanarak devrenin kazancını hesaplarsanız, RF/Ri>>1 koşulu altında

(13)

Olduğunu görürsünüz. Bunu (2) ifadesi ile karşılaştıracak olursanız Kv kazançlı eviren

kuvvetlendiricinin üst kesim frekansının, İK ‘nın üst kesim frekansı olan f2’nin KoLo/Kv katı olduğunu

bulursunuz. Eviren kuvvetlendiricinin Kv kazancı azaldığı oranda üst kesim frekansı büyür. f2’ ile

göstereceğimiz eviren kuvvetlendiricinin üst kesim frekansı ile kazancın çarpımı

(14)

olup bir sabittir. f2’ devrenin, f2 ise İK ‘nın üst kesim frekansıdır. (Ya da bant genişliğidir.). Kazanç

bant genişliğinin sabit olgusu tüm İK devreleri için geçerlidir.

Büyük gerilim kazançları istendiğinde eviren

kuvvetlendiricinin giriş direnci büyük yapılmaz,

zira RF’i 10 MΩ’dan büyük yapmak pratik

değildir ve kazanç arttıkça Ri küçülür ki bu da

devrenin giriş direncidir. Hem büyük kazançlara

hem de büyük giriş dirençlerine olanak tanıyan bir

eviren kuvvetlendirici devresi Şekil-10’da

verilmiştir. Bu devrenin kazancı

K=

Uo

R

=− 2

Ug

R1

R3 R3

1 +

+

R1 R4

olup, R1 değerinden bağımsız olarak R3/R4 oranı ile ayarlanabilirken devrenin giriş direnci R1 olmaya

devam eder. R3, R2, R4 uygun seçilerek kazanç, R1’i küçük seçmeye gerek kalmamaksızın büyük

yapılabilir.

Toplama Devresi

Şekil-11’de verilen bu devrede Uo

(16)

7

veya R1=R2=R3=R için

Uo = −

RF

(U1 + U 2 + U 3 )

R

(17)

girişlerine uygulanan gerilimlerin toplamının negatif işaretlisidir.

Evirmeyen Kuvvetlendirici

Yanda verilen devrenin kazancı

(18)

olup, görüldüğü gibi fazı çevirmez. RF=0 olmadığı sürece kazanç her

zaman 1’den büyüktür. Devrenin üstünlüğü giriş direncinin çok büyük

olmasıdır.

DİKKAT!!

Eviren ve evirmeyen kuvvetlendirici yapısı için ve diğer İK’lı doğrusal kuvvetlendirici yapıları için

geribesleme direnci RF her zaman İK’nın “-“ ucuna bağlanmaktadır. Bu şekilde negatif geribesleme

sağlanarak kazanç belirli bir değere getirilmektedir. RF direnci “+” uca bağlandığında pozitif geribesleme

olacağından İK doğrusal bir kuvvetlendirici olarak çalışmayacaktır. Eviren kuvvetlendiricinin uçlarının

yer değiştirilmesi onu evirmeyen hale getirmez. Dikkat edilirse iki devre için de yapı aynı olup; birinde

toprak bağlanan uca işaret uygulanmakta, diğerinde işaret uygulanan uç toprağa bağlanmaktadır.

Fark Kuvvetlendiricisi

Bu kuvvetlendiricinin çıkış gerilimi

(19)

Olup R2=R4, R1=R3 koşulu sağlandığında;

Uo = −

R2

(U 2 − U1 )

R1

(20)

Olur ki, görüldüğü gibi girişlere uygulanan işaretin farklarını

kuvvetlendirmektedir.

Entegratör

Bu devrenin çıkış gerilimi;

(21)

8

uyarınca giriş geriliminin zaman üzerinden alınmış integralidir ve 1/RC birden büyük olabilen bir

katsayıdır. Giriş kutuplama akımları entegratörde bir hata geriliminin doğmasına neden olur. Bunu

azaltmak için evirmeyen giriş ile toprak arasına R’ye eş bir direnç bağlanabilir. Kutuplama akımlarının

dolayısıyla neden oldukları hatanın küçültülmesi amacıyla giriş katlarında FET kullanılmış İK’ ların

seçimi akıllıca olur.

Benzer şekilde giriş dengesizlik gerilimi de bir hata kaynağıdır, zira bu gerilim de entegre edilmektedir

ya da toplanmaktadır. s domeninde entegratörün kazancı

(22)

olduğundan s=0’da bir kutbu vardır. İK’ nın ve entegratörün Bode diyagramı Şekil-15’te

gösterilmiştir. Görüldüğü gibi İK’nın üst kesim frekansı f2’dir.

(23)

Frekansında (22) ifadesinden görüleceği gibi entegratörün kazancı 1 (dolayısıyla 0 dB)dir. Alçak

frekanslara gidildikçe kazanç artarsa da KOL0’a ulaşıldığı frekansın altına inildiğinde kazanç sabit kalır,

zira İK’ nın kazancı bunun üzerine çıkmaya izin vermez. fe’nin üzerindeki frekanslarda ise

entegratörün kazancı 1’in altına düşer ve fc üzerinde birden küçük bir değerde doymaya girer. Bunun

nedeni fc frekansında İK’ nın kazancı 1 olduğundan entegratör için çıkarılmış olan (22) ifadesinin

geçerliliğini yitirmesidir. Aynı şekilde entegratörün faz diyagramı da verilmiştir. Entegratör fazın 90o

olduğu aralıkta doğrulukla çalışmaktaysa da bunun dışında hata büyür. RC zaman sabitini büyütmenin

Bode diyagramlarını sola doğru kaydırmak demek olduğuna dikkat ediniz.

Şekil 15

Türev Alıcı

Şekil-11’de verilen devreden kolayca

(24)

9

Olduğu gösterilebilir ki çıkış gerilimi giriş geriliminin türevi ile

orantılıdır. Burada detaylarına girmeden bu devrenin osilasyon

yapmaya eğilimli olduğunu ve bu devreyi kullanmanın iyi bir

çözüm olmadığını belirtelim. Fazladan iki eleman gerektiren ve

bu sayede kararlı olması garanti edilebilen bir türev alıcı Şekil17’de verilmiştir. Devrenin kazancı;

(25)

olup genlik Bode diyagramı Şekil-18’de verilmiştir.

iyi bir türev alıcı olarak kullanılabilir.

ve

frekansları arasında devre

Karşılaştırıcı

İK’nın şu ana kadar kapalı çevrimde çalıştırdık. Mantık devrelerinde karşılaştırıcı olarak kullanılan

İK’lar doğrusal kuvvetlendirme şart olmadğından açık çevrimde çalıştırılabilir. Yandaki devre için ;

Vo = KOL.(Vi-VREF)

eşitliği geçerlidir. VCC pozitif besleme, VEE negatif besleme

kaynağıdır. (VCC=+15V, VEE = -15V gibi.) Çıkıştan girişe

herhangi bir geribesleme olmadığından ve KOL açık çevrim

kazancı çok yüksek olduğundan (2.105 gibi) Vi-VREF değeri +10

µV olduğunda bile çıkış gerilimi (2.105).(10.10-6) = +2 V

olacaktır ki bu durum açık çevrimde çalışan İK’ların gürültüye olan duyarlılığını açıklar. Bu farkın

+10 mV olduğunu düşünürsek çıkış gerilimi idealde +2000 V’a çıkmalıdır. Tabi bu pratikte mümkün

değildir; zira İK, kendisini besleyen DC kaynak gerilimlerinin üzerinde bir değer veremez, hatta daha

önce söylediğimiz gibi çıkış değeri besleme gerilimlerinin bir-iki volt aşağısındadır.Devrenin

çalışmasına özetlersek;

Vi > VREF ise; Vo = VCC ve

Vi < VREF ise; Vo = VEE

olur.

Dolayısıyla açık çevrimde çalışan İK’nın çıkışı ya pozitif ya da negatif besleme kaynağının değerini

alır. Giriş uçlarının yerleri değiştirilirse (“+” uç VREF, “-“ giriş Vi olursa)

Vi > VREF ise; Vo = VEE ve

10

Vi < VREF ise; Vo = VCC olacaktır.

DENEY

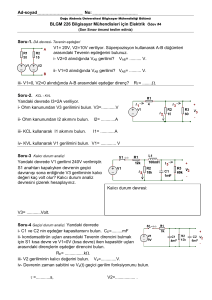

Deney-1:

Yanda verilen devreyi RF=10k Ri=1k ile kurunuz. Girişe Ug 100

mV (tepe), f = 1kHz frekanslı sinusoidal bir gerilim uygulayarak

giriş ve çıkış gerilimlerini aynı anda görüntüleyerek çiziniz.

KANAL-1

VoltDiv

.....

KANAL-2

VoltDiv:......

TimeDiv:.....

Deney-2

Kaynağın frekansını Tablo 1’de verilen değerlere ayarlayarak her adım için Ug ve Uo gerilimlerinin

tepe değerini ölçüp tabloya aktarınız. -3 dB noktası hangi frekanstır?

Tablo 1

Frekans

(kHz)

1

10

100

150

200

250

300

320

Ug (V)

Uo (V)

|K|

Frekans

(kHz)

340

360

380

400

450

500

600

700

Ug (V)

Uo (V)

|K|

Deney-3

RF=100kΩ yaparak frekansı Tablo-2’de verilen değerlere ayarlayarak giriş ve çıkış gerilimlerinin tepe

değerini ölçünüz. -3 dB noktası hangi frekanstır?

11

Tablo 2

Frekans

(kHz)

1

Ug (V)

Uo (V)

Frekans

(kHz)

50

K

10

60

20

70

30

80

40

90

Ug (V)

Uo (V)

K

Deney-4

Ug= 2 V (tepe), f2=1 kHz ayarlayarak Uo, U1, U2

gerilimlerinin tepe değeri ölçünüz.

U1 = ........... V

U2 = ........... V

UO= ........... V

Şekil-20

Deney-5

R direncini kısa devre ve Ug=10V (tepe) yaptıktan sonra Uo geriliminin tepe değerini ölçünüz.

Uo = ........ V

Deney-6

a) Aşağıdaki entegratör devresini kurduktan sonra girişe

tepe değeri 1 V olan 1.6 kHz frekanslı sinusoidal bir gerilim

uygulayarak osiloskopta Ug ve Uo gerilimlerinin dalga

şekillerini aynı anda görüntüleyerek alt alta çiziniz.

Osiloskobu DC kipe alınız.

b) Daha sonra 100 nF’lık kondansatör uçlarına 100 kΩ’lık

bir direnci paralel bağlayarak deneyi tekrarlayınız.

12

Deney-6 (a)

Deney-6 (b)

Deney-7

a) Yandaki türev alıcı devreyi kurunuz. Devrenin girişine 1

kHz frekanslı 1V genlikli kare dalga uygulayıp Uo çıkış

işaretinin ve giriş işaretini alt alta çiziniz. Çıkıştaki

darbelerin genişliğini ölçünüz.

b) R2=100 Ω yaparak deneyi tekrarlayınız.

Deney-7 (a)

Deney-7 (b)

13

Deney-8

R2=1kΩ yaparak girişe tepe değeri 1 V olan üçgen dalga gerilim uygulayarak giriş ve çıkış

gerilimlerini alt alta çiziniz.

SORULAR

DENEY-1: Ölçüm sonuçlarınızı hesaplayarak bulduğunuz sonuçlarla karşılaştırınız.

DENEY-2 ve DENEY-3: Her iki RF değeri için aynı kâğıda genlik ve Bode diyagramını çiziniz. Kazanç

bant genişliği çarpımının sabit kaldığını gösteriniz. Bulduğunuz kazanç bant genişliğini kullandığınız

İK’ nin katalogunda verilmiş olan birim kazanç bant genişliği ile karşılaştırınız.

DENEY-4: Deney sonuçlarınızı hesap sonuçları ile karşılaştırınız.

DENEY-5: Deney sonuçlarınızı katalog bilgilerinden yararlanarak beklenen sonuçlarla karşılaştırınız.

DENEY-6: C2’ye paralel bağlanmış olan direncin etkisini tartışınız. Çıkış işaretinin genliğini

hesapladığınız değerle karşılaştırınız.

DENEY-7: Devrenin genlik ve faz Bode diyagramlarını çiziniz. Devre entegratör olarak hangi

frekansa kadar çalışabilir. Deneyde ölçtüğünüz darbe genişliği ile köşe frekansı arasında bir ilişki var

mı?

DENEY-8: Deney sonuçlarını veriniz ve yorumlayınız.

14