Bölüm 1 Temel Lojik Kapılar

DENEY 1-1 Lojik Kapı Devreleri

DENEYİN AMACI

1. Çeşitli lojik kapıların çalışma prensiplerini ve karakteristiklerini anlamak.

2. TTL ve CMOS kapıların girişi ve çıkış gerilimlerini ölçmek.

GENEL BİLGİLER

Lojik kapılar, iki tip eleman kullanılarak gerçekleştirilir: "İki Kutuplu" ve "Metal Oksit

Yarıiletken (MOS)" elemanlar.

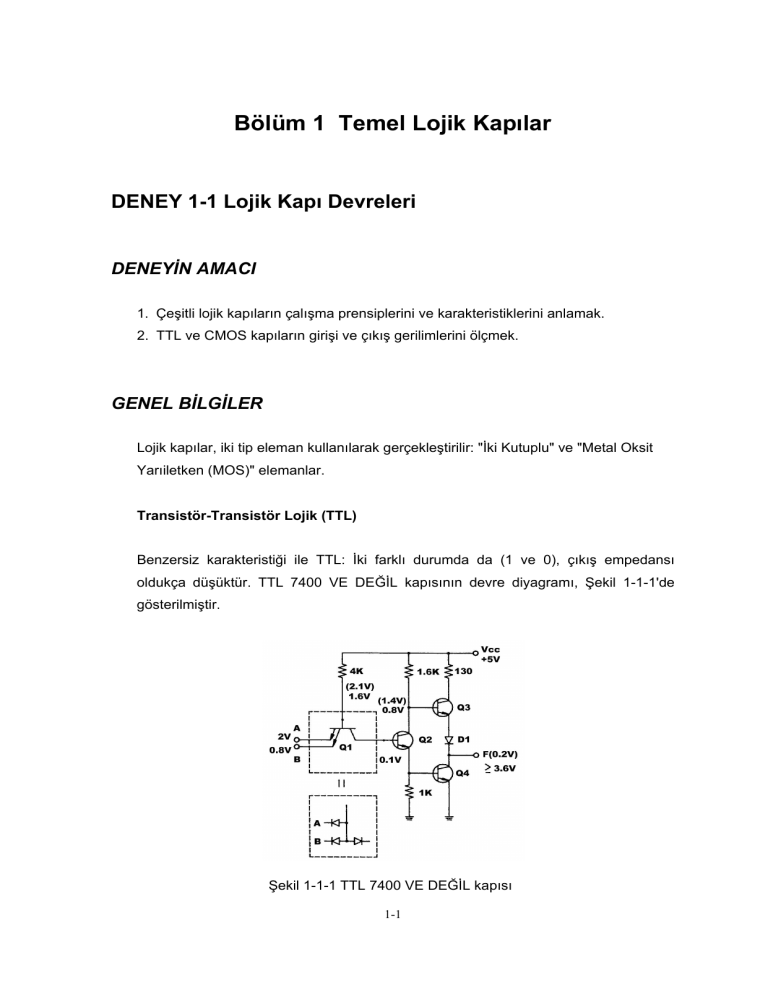

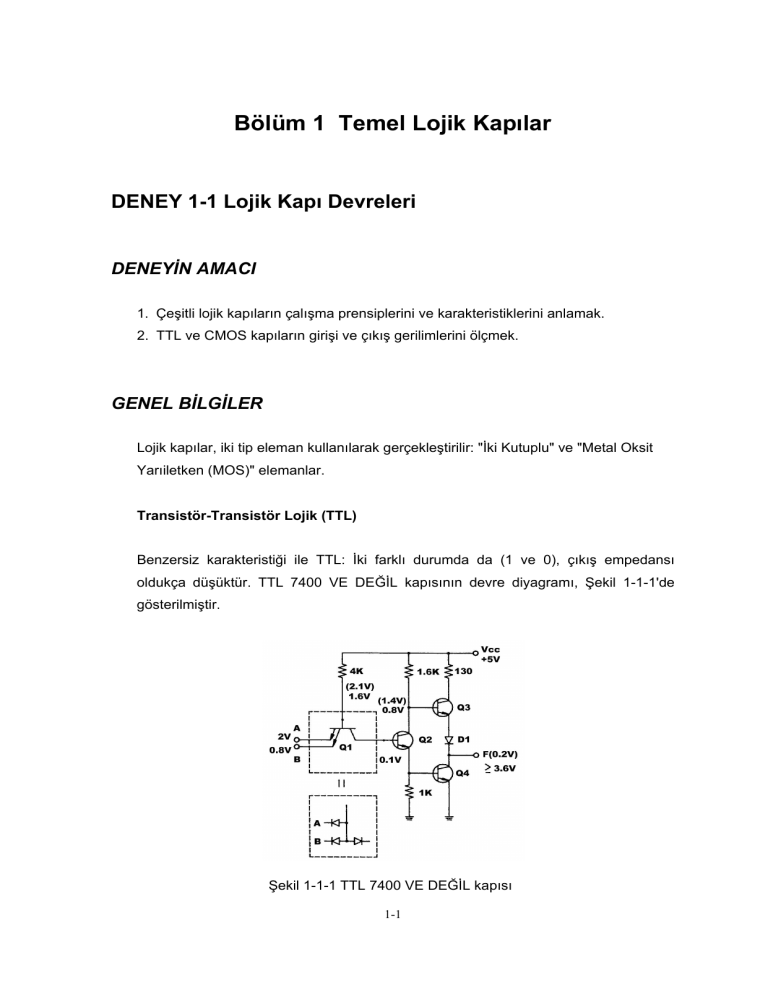

Transistör-Transistör Lojik (TTL)

Benzersiz karakteristiği ile TTL: İki farklı durumda da (1 ve 0), çıkış empedansı

oldukça düşüktür. TTL 7400 VE DEĞİL kapısının devre diyagramı, Şekil 1-1-1'de

gösterilmiştir.

Şekil 1-1-1 TTL 7400 VE DEĞİL kapısı

1-1

Standart bir TTL için alçak ve yüksek seviye giriş gerilimleri, sırasıyla ≤0.8V ve ≥2V

ile sınırlandırılmıştır. Bir giriş 0.8V iken, Q2 transistörünün bazında 0.1V’luk bir gerilim

vardır. Böylece Q4 kesimde (off), Q3 iletimde (on) olur ve çıkış yüksek seviyededir.

Giriş gerilimi 2V iken, Q2’nin bazında 1.4V'luk gerilim olur. Böylece Q2 iletimde (on),

Q3 kesimde (off) olur ve çıkış yüksek seviyededir.

Standart TTL devresi, jonksiyon kapasitansının etkisinden dolayı çok hızlı değildir.

Transistörün baz ve kollektörü arasına “Schottky Diyot” eklenerek, TTL devrelerinin

hızı oldukça artırılabilir. Schottky diyot yaklaşık olarak 0.2V’luk bir öngerilime sahip

olduğu için, transistörün doyma gerilimini ve kesime gitme süresini arttırır. Schottky

diyotu eklenmiş TTL devreleri, "Yüksek Hızlı TTL" olarak adlandırılır ve model

numarasındaki "H" harfi ile belirtilir (74HXX). Schottky diyot eklenmiş düşük güçlü

TTL’ler de, LS harfleriyle belirtilir (74LSXX).

Şekil 1-1-2 Schottky transistör

Schottky transistör, Şekil 1-1-2'de gösterilmiştir. Doyumdayken, kollektör ve emetör

arasındaki gerilim düşümü yaklaşık 0.5V’dur, doyum çok yoğun olmaz ve çalışma hızı

artırılmış olur.

Tek kutuplu MOS elemanlar:

(1) PMOS

(2) NMOS

(3) CMOS

NMOS ile yapılmış bir değilleyici, Şekil 1-1-3'te gösterilmiştir.

1-2

Şekil 1-1-3 NMOS değilleyici

Şekil 1-1-3'te, Q2 yük direnci ve Q1 yükselteç olarak kullanılmıştır. MOSFET’in giriş

empedansı çok yüksek olduğu için (sonsuza yakın), çıkış akımı neredeyse sıfır yada

sadece birkaç +μA kadardır. Bu yüzden MOS, aynı tip yükleri sürmede çok

yeteneklidir ve çok yüksek çıkış yük sayısına (fanout) sahiptir.

CMOS yada "Tümleyen Metal Oksit Yarıiletken", P ve N kanallı MOSFET’lerden elde

edilir. Tipik bir CMOS Şekil 1-1-4’te gösterilmiştir.

Şekil 1-1-4 CMOS değilleyici

Şekil 1-1-4’teki devrede, A= “1” iken, Q2 iletimde ve Q1 kesimde olduğu için çıkış

F=”0” olur. A=“0” iken, tam ters olarak, Q2 kesimde, Q1 iletimdedir ve F=”1” olur. Bu

devre, sırasıyla 1 ve 0’dan sorumlu Q1 ve Q2 MOSFET’lerinden oluşan bir DEĞİL

kapısıdır. Çıkış kapasitesi önemli ölçüde arttırılmıştır.

Tamponlu CMOS’lar, model numarasının sonundaki "B" harfi ile belirtilir. "UB" harfleri

ise tamponsuz bir CMOS’u belirtmektedir. Şekil 1-1-5’te, tamponlu ve tamponsuz

CMOS sembolleri gösterilmiştir.

1-3

MB84000B Serisi

(a) Giriş/çıkış Tamponlu

Diğerleri

(b) Tamponsuz

(c) Çıkış Tamponlu

Şekil 1-1-5 Tamponlu ve tamponsuz IC kapılar

KULLANILACAK ELEMANLAR

1. KL-22001 Temel Elektrik Devreleri Deney Düzeneği

2. KL-26001 Kombinasyonel Lojik Devre Deney Modülü (1)

3. Multimetre

4. DC Güç Kaynağı (0/ +15V)

DENEYİN YAPILIŞI

A. TTL Devresi

1. Şekil 1-1-6'daki bağlantı diyagramı yardımıyla gerekli bağlantıları yapın. U1,

standart seri 7400 VE DEĞİL kapısı ve U2, LS serisi 74LS02 VEYA DEĞİL

kapısıdır.

2. +5VDC sabit güç kaynağını, KL-26001 modülüne bağlayın.

1-4

Şekil 1-1-6 Bağlantı diyagramı (KL-26001 blok c)

3. İlave DC güç kaynağının çıkışını, A1 girişine bağlayın. A1 için giriş gerilimini,

0V~5V arasında sınırlandırın. Tablo 1-1-1'deki giriş dizilerini takip edin, F1

çıkışını ölçün ve kaydedin.

A1

F1

A1

F1

A1

F1

A1

F1

A1

0V

1.5V

2.5V

3.5V

4.5V

0.6V

1.6V

2.6V

3.6V

4.6V

0.7V

1.7V

2.7V

3.7V

4.7V

0.8V

1.8V

2.8V

3.8V

4.8V

0.9V

1.9V

2.9V

3.9V

4.9V

1V

2V

3V

4V

5V

1.1V

2.1V

3.1V

4.1V

1.2V

2.2V

3.2V

4.2V

1.3V

2.3V

3.3V

4.3V

1.4V

2.4V

3.4V

4.4V

F1

Tablo 1-1-1

4. İlave DC güç kaynağının çıkışını, A3 girişine bağlayın. A3 için giriş gerilimini,

0V~5V arasında sınırlandırın. Tablo 1-1-2'deki giriş dizilerini takip edin, F2

çıkışını ölçün ve kaydedin.

1-5

A3

F2

A3

F2

A3

F2

A3

1V

2V

3V

4V

1.1V

2.1V

3.1V

4.1V

1.2V

2.2V

3.2V

4.2V

1.3V

2.3V

3.3V

4.3V

1.4V

2.4V

3.4V

4.4V

1.5V

2.5V

3.5V

4.5V

1.6V

2.6V

3.6V

4.6V

1.7V

2.7V

3.7V

4.7V

1.8V

2.8V

3.8V

4.8V

1.9V

2.9V

3.9V

4.9V

2V

3V

4V

5V

F2

Tablo 1-1-2

B. CMOS Devresi

1. Şekil 1-1-7'deki bağlantı diyagramı yardımıyla gerekli bağlantıları yapın. U5,

standart seri CMOS CD4011’dir. +12VDC sabit güç kaynağını, KL-26001

modülüne bağlayın.

Şekil 1-1-7 Bağlantı diyagramı (KL-26001 blok d)

1-6

2. İlave DC güç kaynağının çıkışını, A5 girişine bağlayın. A5 için giriş gerilimini,

0V’dan başlayarak, 0.5V'luk aralıklarla artırın. Tablo 1-1-3’teki her giriş

gerilimine karşılık gelen Y1 çıkış gerilimini ölçün ve kaydedin.

A5

Y1

A5

Y1

A5

Y1

A5

0V

3.5V

7V

10.5V

0.5V

4V

7.5V

11V

1V

4.5V

8V

11.5V

1.5V

5V

8.5V

12V

2V

5.5V

9V

2.5V

6V

9.5V

3V

6.5V

10V

Y1

Tablo 1-1-3

3. U6, 74HC02 yüksek hızlı CMOS kapısıdır.

4. İlave DC güç kaynağının çıkışını, A8 girişine bağlayın. A8 için giriş gerilimini,

0V’dan başlayarak, 0.5V'luk aralıklarla artırın. Tablo 1-1-4’teki her giriş

gerilimine karşılık gelen Y2 çıkış gerilimini ölçün ve kaydedin.

A8

Y2

A8

Y2

A8

Y2

A8

0V

3.5V

7V

10.5V

0.5V

4V

7.5V

11V

1V

4.5V

8V

11.5V

1.5V

5V

8.5V

12V

2V

5.5V

9V

2.5V

6V

9.5V

3V

6.5V

10V

Tablo1-1-4

1-7

Y2

DENEY 1-2 Eşik Gerilimi Ölçümü

DENEYİN AMACI

1..

şdeğer giriş/çıkış gerilimleri arasındaki ilişkiyi anlamak.

2. TTL ve CMOS kapıların eşik gerilimlerini ölçmek.

GENEL BİLGİLER

Eşik gerilimi yada VT, giriş ve çıkış gerilimlerinin eşit olduğu durumdaki gerilimdir.

Giriş gerilimi, VT’den büyük veya çıkış gerilimi, VT’den küçük ise devre durum

değiştirecektir. VT değeri, lojik kapının türüne bağlı olarak değişir. Bu deneyde,

standart ve LS serisi TTL kapılar ile standart ve HC serisi CMOS kapılarda ölçümler

yapılacaktır.

KULLANILACAK ELEMANLAR

1. KL-22001 Temel Elektrik Devresi Laboratuarı

2. KL-26001 Kombinasyonel Lojik Devre Deney Modülü (1)

3.. Multimet

DENEYİN YAPILIŞI

A. TTL şik Geriliminin Ölçülmesi

1. Şekil 1-2-1'deki bağlantı diyagramı yardımıyla gerekli bağlantıları yapın. +5VDC

sabit güç kaynağını, KL-26001 modülüne bağlayın.

1-8

2. A1 ve F1 uçlarındaki gerilimleri ölçün. U1, standart seri 7400 VE DEĞİL

kapısıdır.

U1 için eşik gerilimi VT=________V

3. A3 ve F2 uçlarındaki gerilimleri ölçün. U2, LS serisi 74LS02 VEYA DEĞİL

kapısıdır.

U2 için eşik gerilimi: VT=________V

Şekil 1-2-1 Bağlantı diyagramı (KL-26001 blok c)

B. CMOS Eşik Geriliminin Ölçülmesi

1. Şekil 1-2-2'deki bağlantı diyagramı yardımıyla gerekli bağlantıları yapın.

+12VDC sabit güç kaynağını, KL-26001 modülüne bağlayın.

2. A5 ve Y1 uçlarındaki gerilimleri ölçün. U5, standart seri CMOS CD4011’dir. U5

için eşik gerilimi: VT=________V

3. A7 ve Y2 uçlarındaki gerilimleri ölçün. U6, 74HC02 yüksek hızlı CMOS

kapısıdır.

U6 için eşik gerilimi: VT=________V

1-9

Şekil 1-2-2 Bağlantı diyagramı (KL-26001 blok d)

1-10

DENEY 1-3 Gerilim/Akım Ölçümü

DENEYİN AMACI

1. TTL ve CMOS kapıların gerilim ve akım karakteristiklerini anlamak.

2. TTL ve CMOS kapıların gerilim ve akım değerlerini ölçmek.

GENEL BİLGİLER

TTL kapıların VIL≤0.8V, VOL≤0.4V, VIH ≥2V, VOH≥2.4V anma gerilim değerleri

kullanılarak IIH, IIL, IOH ve IOL anma akım değerleri belirlenebilir.

Anma gerilim değerleri çıkış lojik seviyesinin doğruluğunu etkilerken, akım değerleri

ise kapıların harici yükleri sürme kapasitesini etkiler.

Bu deneyde, çeşitli lojik kapıların gerilim ve akım değerleri ölçülecek ve

karşılaştırılacaktır. Daha yüksek doğruluk elde etmek için, gerilim ve akım değerlerini

ölçerken mümkün olduğu kadar çok ondalık basamak kaydedin.

KULLANILACAK ELEMANLAR

1. KL-22001 Temel Elektrik Devreleri Deney Düzeneği

2. KL-26001 Kombinasyonel Lojik Devre Deney Modülü (1)

3. Multimetre

1-11

DENEYİN YAPILIŞI

A. TTL I/O Gerilim ve Akımının Ölçülmesi

1. Şekil 1-3-1'deki bağlantı diyagramı ve Şekil 1-3-2'deki devre yardımıyla gerekli

bağlantıları yapın.

Şekil 1-3-1 Bağlantı diyagramı (KL-26001 blok c)

Şekil 1-3-2 TTL gerilim ve akım ölçüm devresi (standart seri)

2. +5VDC sabit güç kaynağını, KL-26002 modülüne bağlayın.

U1'in giriş gerilimini ölçün ve VIL=0.8V olacak şekilde R12'yi ayarlayın. R9'un

uçlarındaki gerilimi ölçün ve kaydedin, VI=_____V. IIL akımını hesaplayın

IIL=VI/100=______mA. U1'in çıkış gerilimini ölçün ve maksimum VOH=______V

ve minimum VOH=_______V değerlerini bulmak için R14'ü ayarlayın.

1-12

3. VOH= 2.4V olacak şekilde R14'ü ayarlayın ve R14 ile toprak arasındaki klipsin

yerine ampermetre bağlayın. IOH değerini ölçün ve kaydedin. IOH=_____mA.

4. R9-R11 ve F1-R13 arasındaki klipsleri çıkartıp, R8-R11 ve F2-R13 arasına

yerleştirin. U2'nin (LS serisi) gerilim ve akım karakteristiklerini ölçün.

Şekil 1-3-3 TTL gerilim ve akım ölçüm devresi (LS serisi)

5. U2'nin giriş gerilimini ölçün ve VIL= 0.8V olacak şekilde R12'yi ayarlayın. R8'in

uçlarındaki gerilimi ölçün ve kaydedin, VI= ___V. IIL akımını hesaplayın

IIL=VI/100=____mA. U2'nin çıkış gerilimini ölçün ve maksimum VOH=_____V ve

minimum VOH=______V değerlerini bulmak için R14'ü ayarlayın.

6. VOH= 2.4V olacak şekilde R14'ü ayarlayın ve R14 ile toprak arasındaki klipsin

yerine ampermetre bağlayın. IOH değerini ölçün ve kaydedin. IOH=_____mA.

7. Şekil 1-3-4'teki bağlantı diyagramı ve Şekil 1-3-5'teki devre yardımıyla gerekli

bağlantıları yapın. VIH= 2 olacak şekilde R12'yi ayarlayın. R9'un uçlarındaki

gerilimi ölçün, VI=_______V. IIH akımını hesaplayın IIH=VI/100=________mA.

8. U1'in çıkış gerilimini ölçün ve maksimum VOL= ________V ve minimum

VOL=________V değerlerini bulmak için R14'ü ayarlayın.

9. VOL= 0.4V olacak şekilde R14'ü ayarlayın ve R14 ile +5V arasındaki klipsin

yerine ampermetre bağlayın. IOL değerini ölçün ve kaydedin. IOL=______mA.

1-13

Şekil 1-3-4 Bağlantı diyagramı (KL-26001 blok c)

Şekil 1-3-5 TTL gerilim ve akım ölçüm devresi (standart seri)

10. R9-R10 ve F1-R13 arasındaki klipsleri kaldırıp, R8-R10 ve F2-R13 arasına

yerleştirin.

11. VIH= 2V olacak şekilde R12'yi ayarlayın. R8'in uçlarındaki gerilimi ölçün,

VI=_______V. IIH akımını hesaplayın IIH=VI/100=________mA.

1-14

Şekil 1-3-6 TTL gerilim ve akım ölçüm devresi (LS seri)

12. U2'nin çıkış gerilimini ölçün ve maksimum VOL= _______V ve minimum

VOL=_______V değerlerini bulmak için R14'ü ayarlayın.

13. VOL= 0.4V olacak şekilde R14'ü ayarlayın ve R14 ile +5V arasındaki klipsin

yerine ampermetre bağlayın. IOL değerini ölçün ve kaydedin. IOL=_____mA.

B. CMOS Gerilim ve Akımının Ölçülmesi

1. Şekil 1-3-7'deki bağlantı diyagramı ($ işaretli klips hariç) ve Şekil 1-3-8'deki

devre yardımıyla gerekli bağlantıları yapın.

2. KL-22001 Düzeneğindeki +12VDC sabit güç kaynağını, KL-26002 modülüne

bağlayın. V+’yı, +12V'a bağlayın.

3. VIL gerilimi 3.6V olacak şekilde R19'u ayarlayın. R16'nın uçlarındaki gerilimi

ölçün, VI=_______V. IIL akımını hesaplayın IIL=VI/100=________mA.

4. Y1 ucundaki gerilimi ölçün ve maksimum VOH= _______V ve minimum

VOH=________V değerlerini bulmak için R21'i ayarlayın.

5. VOH gerilimi 10.8V olacak şekilde R21'i ayarlayın ve # işaretli klipsin yerine

ampermetre bağlayın. IOH değerini ölçün ve kaydedin IOH=_______mA.

1-15

6. VIH gerilimi 8.4V olacak şekilde R19'u ayarlayın. # işaretli klipsi çıkartın ve $

işaretli klipsi yerleştirin. R16'nın uçlarındaki gerilimi ölçün, VI= ______V. IIH

akımını hesaplayın IIH=VI/100=________mA.

7. Y1 ucundaki gerilimi ölçün ve maksimum VOL= _______V ve minimum

VOL=________V değerlerini bulmak için R21'i ayarlayın.

8. VOL gerilimi 1.2V olacak şekilde R21'i ayarlayın. $ işaretli klipsin yerine

ampermetre bağlayın. IOL değerini ölçün ve kaydedin. IOL=________mA.

Şekil 1-3-7 Bağlantı diyagramı (KL-26001 blok d)

Şekil 1-3-8 CMOS gerilim ve akım ölçüm devresi

1-16

DENEY 1-4 Temel Lojik Kapıların Karakteristikleri

DENEYİN AMACI

1. Temel lojik kapıların sembollerini ve karakteristiklerini anlamak.

2. Temel lojik kapıların karakteristiklerini ölçmek.

GENEL BİLGİLER

Temel lojik kapıların giriş ve çıkış karakteristikleri aşağıda tanımlanmıştır:

VOH = Yüksek seviye çıkış gerilimi

IOH = Yüksek seviye çıkış akımı

VOL = Düşük seviye çıkış gerilimi

IOL = Düşük seviye çıkış akımı

VIH = Yüksek seviye giriş gerilimi

IIH = Yüksek seviye giriş akımı

VIL = Düşük seviye giriş gerilimi

IIL = Düşük seviye giriş akımı

TTL kapıların karakteristikleri, CMOS kapılarınkilerden farklıdır. Aynı şekilde, kapılara

bağlanan yük ve akım sınırlama dirençleri de farklıdır. Örneğin bir VE kapısı ve bir

VEYA kapısı durumunda:

1. TTL ve CMOS Kapıların YÜKSEK ve ALÇAK Girişleri

CMOS kapıların girişi 10KΩ'luk bir dirence bağlanırken, TTL girişleri, 1KΩ'luk

dirence bağlanır.

TTL kapıların "ALÇAK" girişi

CMOS kapıların "ALÇAK" girişi

LS serisi TTL kapılar için direnç değeri yaklaşık olarak 5KΩ’dur. Eğer bir TTL

VEYA kapısının X girişi topraklanırsa, genişleme kontrolünü imkansız yapacak

şekilde, F çıkışı A girişine eşit olur (F=A).

1-17

Eğer direnç topraklanmışsa ve X girişinde sinyal yoksa, bu durum X’in

topraklanmasına eşdeğerdir ve F= A’dır. Gerekirse, F= A+X olacak şekilde, X

girişine bir sinyal eklenebilir. Çıkış, X tarafından kontrol edilebilir.

2. VE Kapısı

TTL VE kapıları, açıkken (girişine sinyal bağlı değil) yada besleme gerilimine bir

direnç bağlıyken, yüksek durumdadır. CMOS VE kapıları, besleme gerilimine en

az 10KΩ’luk bir direnç bağlıyken yüksek durumdadır.

TTL kapıların "YÜKSEK" girişi

CMOS kapıların "YÜKSEK" girişi

"Doğruluk Tablosu", bir lojik kapının, ideal şartlar altında, girişlerine karşılık gelen

çıkışları gösteren bir tablodur.

3. VEYA Kapısı

DURUM

UM

İRİŞLER

ÇIKIŞ

Açıklama

A

B

F

0

0

0

0

A=0 B=0 iken, çıkış F=0

1

0

1

1

A=0 B=1 iken, çıkış F=1

2

1

0

1

A=1 B=0 iken, çıkış F=1

3

1

1

1

A=1 B=1 iken, çıkış F=1

Boolean ifadesi: F = AB + AB + AB = A + B

1-18

4. VE Kapısı

DURUM

UM

İRİŞLER

ÇIKIŞ

Açıklama

A

B

F

0

0

0

0

A=0 B=0 iken, çıkış F=0

1

0

1

0

A=0 B=1 iken, çıkış F=0

2

1

0

0

A=1 B=0 iken, çıkış F=0

3

1

1

1

A=1 B=1 iken, çıkış F=1

Boolean ifadesi: F=AB

5. DEĞİL (NOT) Kapısı

DURUM

UM

İRİŞ

ÇIKIŞ

Açıklama

A

F

0

0

1

A=0 iken, çıkış F=1

1

1

0

A=0 iken, çıkış F=0

Boolean ifadesi: F = A

6. ÖZEL VEYA (XOR) Kapısı

DURUM

UM

İRİŞLER

ÇIKIŞ

A

B

F

0

0

0

0

1

0

1

1

2

1

0

1

3

1

1

0

A=B iken, çıkış F=0

A≠B iken, çıkış F=1

Boolean ifadesi: F = AB + AB = A ⊕ B

1-19

7. VE DEĞİL (NAND) Kapısı

VE DEĞİL kapısının çıkışı, VE kapısının tamamen tersidir.

DURUM GİRİŞLER

ÇIKIŞ

Açıklama

A

B

F

0

0

0

1

A=0 B=0 iken, çıkış F=1

1

0

1

1

A=0 B=1 iken, çıkış F=1

2

1

0

1

A=1 B=0 iken, çıkış F=1

3

1

1

0

A=1 B=1 iken, çıkış F=0

Boolean ifadesi: F = AB

8. VEYA DEĞİL (NOR) Kapısı

VEYA DEĞİL kapısının çıkışı, VEYA kapısının tamamen tersidir.

DURUM GİRİŞLER

ÇIKIŞ

Açıklama

A

B

F

0

0

0

1

A=0 B=0 iken, çıkış F=1

1

0

1

0

A=0 B=1 iken, çıkış F=0

2

1

0

0

A=1 B=0 iken, çıkış F=0

3

1

1

0

A=1 B=1 iken, çıkış F=0

Boolean ifadesi: F = A + B = A× B

Bu doğruluk tabloları, pozitif gerilimin lojik “1”, negatif gerilimin lojik “0” durumlarını

temsil ettiği, pozitif lojik esasına dayalıdır. Negatif lojik durumunda çıkışlar ters

çevrilecektir.

Aşağıda, pozitif ve negatif lojik için verilen VEYA kapısı doğruluk tablolarını

karşılaştırın:

1-20

DURUM

UM

İRİŞLER

ÇIKIŞ

A

B

F

0

0

0

0

1

0

1

2

1

3

1

DURUM

GİRİŞLER

R

ÇIK Ş

A

B

F

0

1

1

1

1

1

1

0

0

0

1

2

0

1

0

1

1

3

0

0

0

Negatif lojik için verilen VEYA kapısı doğruluk tablosunun, pozitif lojik VE kapısına

eşdeğer olduğuna dikkat edin.

KULLANILACAK ELEMANLAR

1. KL-22001 Temel Elektrik Devreleri Deney Düzeneği

2. KL-26001 Kombinasyonel Lojik Devre Deney Modülü (1)

3. Osiloskop

DENEYİN YAPILIŞI

A. VE Kapısı Karakteristiklerinin Ölçülmesi

1. Şekil 1-4-1'deki bağlantı diyagramı ve Şekil 1-4-2'deki devre yardımıyla gerekli

bağlantıları yapın. +5VDC sabit güç kaynağını, KL-26002 modülüne bağlayın.

1-21

Şekil 1-4-1 Bağlantı diyagramı (KL-26001 blok c)

Şekil 1-4-2 VE ve VEYA kapılarının eşdeğer devreleri

2. A1 ve A2 girişlerini, SW0 ve SW1 veri anahtarlarına, F3 çıkışını ise L0 Lojik

Göstergesine bağlayın. Aşağıdaki giriş dizilerini takip edin ve çıkışları kaydedin.

DURUM

A2

A1

0

0

0

1

0

1

2

1

0

3

1

1

F3

3. A2 girişine, Fonksiyon Üretecinden 10Hz'lik TTL seviye kare dalga uygulayın.

Aşağıdaki A1'in giriş koşullarını takip edin (Saat Üretecinden 1Hz'lik kare

alarak). Giriş ve çıkış dalga şekillerini ölçün ve kaydedin.

1-22

(1) A1=0

(2) A1=1

(3) A1=1 Hz

A2

A2

A2

F3

F3

F3

B. VEYA Kapısı Karakteristiklerinin Ölçümü

1. KL-26001 blok c'deki U2, bu kısmda kullanılacaktır.

2. A3, A4 girişlerini, SW0, SW1 veri anahtarlarına ve F4 çıkışını L1 Lojik

Göstergesine bağlayın. Aşağıdaki giriş dizilerini takip edin ve F4 çıkışını

kaydedin.

DURUM

A4

A3

0

0

0

1

0

1

2

1

0

3

1

1

F4

3. A4 girişine, Fonksiyon Üretecinden 10Hz'lik TTL seviye kare dalga uygulayın.

Aşağıdaki A3'ün giriş koşullarını takip edin (Saat Üretecinden 1Hz'lik kare

alarak). Giriş ve çıkış dalga şekillerini ölçün ve kaydedin.

1-23

(1) A3=0

(2) A3=1

(3) A3=1 Hz

A4

A4

A4

F4

F4

F4

C. DEĞİL Kapısı Karakteristiklerinin Ölçülmesi

1. U3'ün C1 girişini ve F6 çıkışını sırasıyla SW0 veri anahtarına ve L1 Lojik

Göstergesine bağlayın. Aşağıdaki giriş dizilerini takip edin ve çıkışları kaydedin.

DURUM

C1

0

0

1

1

F6

2. F6'yı C2'ye bağlayın. F7 çıkışını, L2 Lojik Göstergesine bağlayın. Aşağıdaki

giriş dizilerini takip edin ve çıkışları kaydedin.

DURUM

C2

0

0

1

1

F7

D. VE DEĞİL Kapısı Karakteristiklerinin Ölçülmesi

1. Aşağıdaki ölçümlerde U1 kullanılacaktır. A1,A2 girişlerini, SW0, SW1 veri

anahtarlarına, F1 çıkışını L1 Lojik Göstergesine bağlayın. Aşağıdaki giriş giriş

dizilerini takip edin ve çıkışları kaydedin.

1-24

DURUM

A2

A

0

0

0

1

0

1

2

1

0

3

1

1

F1

2. A2 girişine, Fonksiyon Üretecinden 10Hz'lik TTL seviye kare dalga uygulayın.

Aşağıdaki A1'in giriş koşullarını takip edin (Saat Üretecinden 1Hz'lik kare

alarak). Giriş ve çıkış dalga şekillerini ölçün ve kaydedin.

(1) A1=0

(2) A1=1

(3) A1=1 Hz

A2

A2

A2

F1

F1

F1

E. VEYA DEĞİL Kapısı Karakteristiklerinin Ölçülmesi

1. Aşağıdaki ölçümlerde U2 kullanılacaktır. A3,A4 girişlerini, SW0,SW1 veri

anahtarlarına, F2

çıkışını L1 Lojik Göstergesine bağlayın. Aşağıdaki giriş

dizilerini takip edin ve çıkışları kaydedin.

DURUM

A4

A

0

0

0

1

0

1

2

1

0

3

1

1

1-25

F2

2. A4 girişine, Fonksiyon Üretecinden 10Hz'lik TTL seviye kare dalga uygulayın.

Aşağıdaki A3'ün giriş koşullarını takip edin (Saat Üretecinden 1Hz'lik kare

alarak). Giriş ve çıkış dalga şekillerini ölçün ve kaydedin.

(1) A3=1

(2) A3=0

(3) A3=1 Hz

A4

A4

A4

F2

F2

F2

F. ÖZEL VEYA Kapısı Karakteristiklerinin Ölçülmesi

1. Aşağıdaki ölçümlerde U4 kullanılacaktır. C4,C5 girişlerini SW0,SW1 veri

anahtarlarına, F9

çıkışını L1 Lojik Göstergesine bağlayın. Aşağıdaki giriş

dizilerini takip edin ve çıkışları kaydedin.

DURUM

C

C5

5

C

0

0

0

1

0

1

2

1

0

3

1

1

F9

2. C4 girişine, Fonksiyon Üretecinden 10Hz'lik TTL seviye kare dalga uygulayın.

Aşağıdaki C5'in giriş koşullarını takip edin (Saat Üretecinden 1Hz'lik kare

alarak). Giriş ve çıkış dalga şekillerini ölçün ve kaydedin.

1-26

(1) C5=1

(2) C5=0

(3) C5=1 Hz

C4

C4

C4

F9

F9

F9

1-27

DENEY 1-5 Lojik Kapılar Arasında Arayüz

DENEYİN AMACI

1. Arayüz bağlantı tekniklerini anlamak.

2. TTL'den CMOS'a ve CMOS'tan TTL'e arayüz devresi oluşturmak.

GENEL BİLGİLER

TTL ve CMOS, en sık kullanılan lojik kapılardır. Özellikleri aşağıda gösterilmiştir.

TTL

Besleme gerilimi

CMOS

+5V±0.25V 3~18V

Düşük seviye giriş gerilimi VIL ≤ 0.8V

≤1.5V

Yüksek seviye giriş gerilimi VIH ≥2.0V

≥3.5V

Düşük seviye çıkış gerilimi VOL ≤0.4V

0V

Yüksek seviye çıkış akımı VOH ≥2.4V

5V

Düşük seviye giriş akımı

IIL

≤1.6mA

≤0.1µA

Yüksek seviye giriş akımı

IIH

≤40µA

≤0.1mA

Düşük seviye çıkış akımı

IOL ≥16mA

Yüksek seviye çıkış akımı IOH ≥0.4µA

≥1mA

≥0.1mA

Tablodan, CMOS kapının giriş gerilimi gereksiniminin, TTL kapının çıkış gerilimi

kapasitesinden daha yüksek olduğu görülmektedir.

Eğer bir TTL kapı, bir CMOS kapıyı sürmek için kullanılırsa, TTL’in çıkış gerilimi,

CMOS’un giriş gerilimi gereksimini karşılayabilmek için, arttırılmadır. Öte yandan

TTL’i sürmek için CMOS kullanıldığı zaman, CMOS’un çıkış akımı arttırılmalıdır. Bu

yüzden, bir arayüz devresi gerçekleştirmeden önce, veri sayfaları dikkatlice

incelenmelidir.

1-28

Şekil 1-5-1’de gösterildiği gibi, TTL tarafından sürülen CMOS’un giriş gerilimini

arttırmak için, besleme gerilimine bağlı bir RX direnci eklenebilir. RX değer aralığı,

standart seri TTL için 390Ω~4.7KΩ, LS serisi için 820Ω ~12KΩ ‘dur.

Bir TTL kapı CMOS tarafından sürüleceği zaman, CMOS’un çıkış akımını arttırmak

için araya bir tampon eklenmelidir. Paralel olarak bağlanmış iki standat CMOS, bir LS

serisi TTL kapısını sürebilir.

Şekil 1-5-1 TTL-CMOS arayüz devresi

KULLANILACAK ELEMANLAR

1. KL-22001 Temel Elektrik Devreleri Deney Düzeneği

2. KL-26001 Kombinasyonel Lojik Devre Deney Modülü (1)

3. Multimetre

DENEYİN YAPILIŞI

A. TTL-CMOS Arayüzü

1. Şekil 1-5-2'deki bağlantı diyagramına göre gerekli bağlantıları yapın. U1,

standart seri TTL kapısıdır.

2. (R13+R14) 220Ω olacak şekilde R14'ü ayarlayın.

1-29

3. +5VDC sabit güç kaynağını, KL-26001 modülünün sağ üst köşesinde

bulunan +12VDC ve +5VDC uçlarına bağlayın.

Bu şekilde, hem TTL hemde CMOS kapılarına +5V besleme gerilimi sağlanmış

olur. A1 girişini, SW0 veri anahtarına bağlayın. A1 için aşağıda verilen giriş

koşullarını takip edin. F1, A5 ve Y1 uçlarındaki gerilimleri ölçün ve kaydedin.

A1

F1

A5

Y1

0

1

4. Klips kullanarak, R14'ü +5V'a bağlayın. 3. adımı tekrarlayın.

A1

F1

A5

Y1

0

1

Şekil 1-5-2 Bağlantı diyagramı (KL-26001 blok c ve d)

B. CMOS-TTL Arayüzü

1. Aşağıdaki ölçümlerde U7 kullanılacaktır. Şekil 1-5-2'deki bağlantı diyagramı

yardımıyla gerekli bağlantıları yapın.

1-30

2. U7'nin Y8 çıkışını, U1'in A1 girişine ve C8'i, SW1 veri anahtarına bağlayın. C8

için aşağıda verilen giriş koşullarını takip edin. Y8, A1 ve F1 uçlarındaki

gerilimleri ölçün ve kaydedin.

C8

Y8

A1

F1

0

1

3. Klipsleri kullanarak C6, C7 ve C8'i paralel bağlayın. 2. adımı tekrarlayın.

C8

Y8

A1

F1

0

1

4. Y8'i, U3'ün C1, C2, ve C3 girişlerine bağlayın. U3'ün F6, F7 ve F8 çıkışlarını

paralel olarak bağlayın. 2. adımı tekrarlayın.

C8

Y8

0

1

1-31

C1

F6