6th International Advanced Technologies Symposium (IATS’11), 16-18 May 2011, Elazığ, Turkey

FPGA Tabanlı DGM Sinyalinin Üretilmesi ve

Bir Eviriciye Uygulanması

A. Diker1, Ö. F. Alçin2, M. Gedikpınar3

1

aykutdiker@gmail.com

University of Firat, Elazig/Turkey, ofalcin@firat.edu.tr

3

University of Firat, Elazig/Turkey, mgedikpinar@firat.edu.tr

2

FPGA-Based PWM Signal Generation and

Application of An Inverter

Abstract—In this study, PWM (Pulse Width Modulation) signals

have been generated with FPGA. Dead-time signals has been

created by using software. VHDL (Very-high-speed integrated

circuits Hardware Description Language) has been chosen to

prepare program. Prepared VHDL code was synthesized and

installed to FPGA by using Xilinx ISE environment. In

experimental study, the PWM signals were applied to half bridge

inverter and results were given. This produced FPGA-based

PWM signals provides a low-cost software and hardware.

Keywords—FPGA, PWM, Half-Bridge Inverter, Dead-time.

I. GİRİŞ

Eviriciler, güç elektroniği teknolojisinin gelişimiyle

birlikte birçok alanda kullanılmıştır. Bu gelişme

araştırmacıların ilgisini çekmektedir. Evirici, DA/AA

değişikliği yapan bir çeviricidir [1]. Son yıllarda Darbe

Genişlik Modülasyon (DGM-Pulse Width Modulation, PWM)

eviriciler ve DGM doğrultucular gibi yarı iletken güç

devreleri, enerji depolama tesisleri, iletişim sistemleri ve

elektrikli araçlar için çok önemli hale gelmiştir. Çünkü bu

sistemler için daha kaliteli güç kaynağı, hızlı cevap ve kontrol

yeteneği bu sistemler için gereklidir [2]. Ayrıca sayısal kontrol

teknikleri, modern güç elektroniği uygulamalarında yaygın

olarak kullanılmaktadır. Sayısal kontrollü güç elektroniği

devrelerinin tasarımında; örnekleme oranı, yazılım

taşınabilirliği, yeniden kullanılabilirlik, çevre birimlerinin

uyumu ve her bir mikroişlemciye özgü kayıtçı ayarlarının

saklanması gibi çeşitli sorunlarla karşılaşılmaktadır. Bu

sorunlar, Alan Programlanabilir Kapı Dizisi (Field

Programmable Gate Array, FPGA) ile azaltılabilir [3]. FPGA

teknolojisi, düşük maliyeti ve hızlı gerçekleştirme süresi ile

programlanabilen, tekrar yapılandırılabilen sayısal sistemlerin

uygulanması için önemli bir cihaz teknolojisi haline gelmiştir

[4]. FPGA teknolojisindeki ilerleme, verimli sayısal sinyal

işleme, tüm sistem ve alt sistemleri içeren tek devre

çözümlerinde kullanılmasını sağlamıştır [5]. Aynı zamanda

FPGA esnek donanım yapısı, yüksek hesaplama hızı gibi

üstünlüklere de sahiptir [6]. Güç anahtarlarının anahtarlama

esnasında kısa devre olmasını önlemek için DGM kontrollü

eviricilerde ölü-zaman kullanılmaktadır. Ölü zamanın

kullanılması çıkış geriliminde kayıplara ve akım bozulmalarını

içeren olumsuzluklara sahiptir. Bu olumsuzluklar, anahtarlama

frekansının yükselmesi ve gerilimin azalması ile ilgilidir [7].

Eviricilerde aynı hatta bağlı anahtarlar, biri diğerinden

tümleyenli üretilmiş DGM işareti ile sürüldüğünde, sürücü

işaretin düşen ve yükselen kenarlarında anahtar hızları yavaş

kaldığı için üstteki anahtar henüz tıkamaya gitmeden alttaki

anahtar tetiklenmiş olur. Bu durumda DA besleme hattı bu

anahtar grubu tarafından kısa devre olmakla birlikte anahtarlar

da kısa devre akımından etkilenerek zarar görmektedir [8].

Bu uygulamada yazılım tabanlı donanım (FPGA)

kullanılarak yarım köprü bir evirici için gerekli DGM

sinyalleri üretilmiştir. Makalenin işleyişi şu şekildedir: İkinci

bölümde eviriciler hakkında genel bilgi verilmiştir. Üçüncü

bölümde ise, uygulamada kullanılan kart hakkında bilgiler

aktarılmıştır. Hazırlanan deneysel düzenek dördüncü bölümde

tanıtılmıştır. Sonuç bölümünde deneyde elde edilen veriler

verilmiştir.

II. EVİRİCİLER

Eviriciler DA kaynaklarından beslenerek yüke A.A güç

sağlayan güç elektroniği devreleridir. Eviricilerde genel amaç;

istenen frekans ve genlikte A.A çıkış üretmenin yanında A.A

ile beslenmesi zorunlu olan yükleri D.A kaynaklardan

besleyebilmektir. Eviricilerin çıkış gerilim dalga şeklinin

sinüsoidal olması istenir. Ancak pratikte kullanılan eviricilerin

çıkış dalga şekilleri kare veya kare dalgaya benzeyen olup bu

dalga şekilleri oldukça yüksek oranda harmonikler

içermektedir. Düşük ve orta güçlü uygulamalarda kare dalga

veya basamaklı kare dalga biçiminde gerilim dalga şekilleri

çıkış olarak kabul edilebilir. Fakat yüksek güçlü

uygulamalarda mümkün olduğu kadar harmoniği az olan

sinüsoidal bir dalga biçimi tercih edilmektedir.

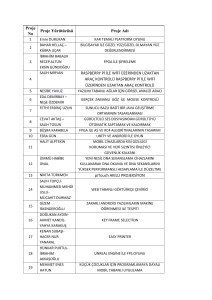

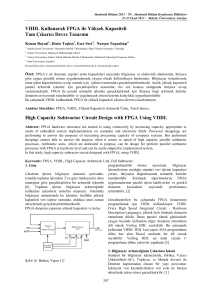

Şekil 1(a)’da bir yarım köprü evirici devresi gösterilmiştir.

Bu devrede kullanılan anahtarlar birbirinin zıttı şeklinde

çalışmalıdır. Yani bir anahtar iletimde ise diğeri kesimde

olmalıdır. Anahtarların her ikisinin iletimde olması

durumunda kaynak kısa devre olur ve evirici zarar görür. Her

iki anahtar kesimde olursa, boşluk diyotları anahtarların zarar

görmesini engeller. Şekil 1(a)’da gösterilen yapıda orta uçlu

gerilim kaynağına ihtiyaç duyulmaktadır. Orta ucu elde etmek

için birbirlerine seri bağlı ve aynı değere sahip olan iki kaynak

kullanılır. Verilen devrede T 1 anahtarı iletimde olduğunda yük

101

A. Diker, Ö. F. Alçin, M. Gedikpınar

VA0 Vdc / 2 ve T 2 anahtarlanırsa yük

Vdc / 2 olur. Çıkış geriliminin dalga şekli

Şekil 2: İdeal ve ölü-zaman eklenmiş DGM sinyalleri.

üzerindeki gerilim

gerilimi

VA0

Şekil 1(b)’de gösterilmektedir [9].

T1

+

-

VDC/2

Yük

0

VDC

VDC/2

A. FPGA

FPGA’lar ilk kez Xilinx firması tarafından piyasaya

sürülmüştür. Ağ oluşturma, sayısal sinyal işleme gibi pek çok

uygulama alanında başarı ile kullanılmıştır [12]. Herhangi bir

mantıksal devrenin FPGA ile; düşük maliyette geliştirilmesi

ve FPGA’nın doğasında olan alan programlama esnekliği

sayesinde, FPGA teknolojisi göz alıcı biçimde büyümüş ve bu

özellikleri FPGA nın çok geniş ölçekli entegre devre (Very

Large Scala Integration, VLSI) aygıtlar arasında popüler

olmasına yol açmıştır [13,14].

FPGA’lar herhangi bir

sayısal devreyi ya da sistemi gerçeklemek için elektriksel

olarak programlanabilen yarı-hazır silikon aygıtlardır.

Programlanabilme terimi; silikon aygıtın üretildikten sonra

programlanabilme yeteneğini gösterir [15]. Sayısal sistemlerde

FPGA’ların kullanılması zamanla gelişen sanayinin donanım

güncellemesini karşılamak için gerekli olan zaman ve maliyeti

azaltır [16].

D1

I0

A

+

-

III. FPGA

T2

D2

(a)

VA0

VDC/2

t

VDC/2

Ara bağlantı

Eviricilerde kullanılan anahtarlama elemanları özellikle

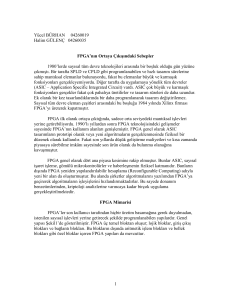

kesim anında gecikme zamanına sahiptirler. Anahtarların eş

zamanlı iletime girmemesini sağlamak için anahtarların kapı

sinyaline ölü-zaman eklenir. Bu ölü-zaman gecikmesi Şekil

2’de gösterilmiştir. Ancak ölü zaman, ideal olmayan güç

elemanları sebebiyle çıkış akımında bozulmalara neden

olmaktadır [10,11].

Mantık bloğu

Şekil 1: (a) Yarım köprü evirici devresi , (b) Çıkış gerilimi

dalga şekli.

T 1 ideal

Şekil 3: FPGA mimarisi.

T 2 ideal

TDT

TDT

T1 gerçek

T2 gerçek

G/Ç Blokları

Ara Bağlantı Hattı

(b)

TDT

TDT

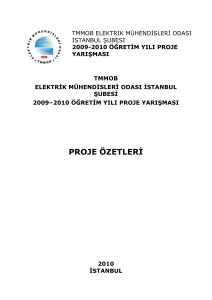

FPGA programlanabilir tümleşik devrelerdir. Tasarımcının

ihtiyacı olan mantıksal fonksiyonları gerçekleştirebilmesi

amacıyla, kullanıldığı yerde programlanabilir olarak üretilirler.

Kullanıcının tasarladığı mantıksal devreye göre, mantıksal

bloklar, aralarındaki bağlantılar ve giriş/çıkış blokları

programlanır [17].

Farklı FPGA üretici firmalarının kendine özgü mimarileri

olmasına rağmen genelde FPGA üç ana bileşenden oluşur. Bu

bileşenler,

birleşimsel/sıralı

mantık

fonksiyonları

gerçekleştirebilen mantık bloklar, dış dünya ile iletişim için

G/Ç blokları ve bloklar arasında bağlantı kuran, sabit ya da

programlanabilen yönlendirme hatları şeklinde sıralanır.

Genel bir FPGA mimarisi Şekil 3’de verilmiştir. Mantık

bloklar ve G/Ç blokları arasındaki bağlantı, yönlendirme

hatları ve ara bağlantının (anahtar matrislerinin)

programlanması ile sağlanır [18,19]. Üreticiler, kendi FPGA

mimarilerinin programlanabilirlik özelliğini sağlamak için

SRAM (Statik RAM), EPROM, sigorta ve karşıt sigorta (Anti

102

FPGA Tabanlı DGM Sinyalinin Üretilmesi ve Bir Eviriciye Uygulanması

fuse) gibi farklı programlama çözümleri kullanılmaktadırlar

[14].

B. UYGULAMA GELİŞTİRME KARTI

Bu çalışmada Digilent’s BASYS devre kartı kullanılmıştır.

Kullanılan kartın üstten görüntüsü Şekil 4’ de gösterilmiştir.

IV. DENEYSEL ÇALIŞMA

Deneysel çalışmada; FPGA ile üretilen DGM sinyalleri

yarım köprü evirici devresine uygulanmıştır. Şekil 6’da

hazırlanan deneysel düzeneğin görüntüsü verilmiştir.

Düzenekte izolasyon devresinde 6N136 opto-coupler, güç

devresinde IRFP064N güç mosfetleri ve FPGA için

SPARTAN 3E Digilent’s BASYS uygulama geliştirme kartı

kullanılmıştır. Düzeneği test etmek için 25W’lık bir lamba

yükü seçilmiştir.

Şekil 4: BASYS uygulama geliştirme kartı.

Bu kartın özellikleri [20]:

Xilinx Sprartan 3E FPGA (XC3S100E-100,000 kapı)

JTAG programlama portu

XCF02S Xilinx Platform Flash ROM (FPGA

konfigürasyonunu saklamak için)

8 adet LED, 4 adet buton, 8 adet kaymalı anahtar, 4

adet 7 segmentli display, PS/2 ve VGA portu

Kullanıcı tarafından seçilebilir (25/50/100 MHz)

osilatör ve ikinci osilatör için soket

G/Ç ve çevresel modül bağlantısı için, 4 adet 6-pinli

port

Tüm G/Ç portlarında sinyallerinde elektro-statik

deşarj (ESD) ve kısa devre koruması mevcuttur.

Şekil 6: Deney düzeneği.

Şekil 7’de FPGA ile DGM sinyalleri üretimi için blok

şema verilmiştir.

Veri

(8-Bit)

Veri Kayıtçısı

DGM1

Saat

Şekil 5’de ise Digilent’s BASYS devre kartının blok

diyagramı verilmiştir.

Sayıcı

Karşılaştırma

DGM2

Ölü Zaman

Üreteci

FPGA

Şekil 7: İki kanallı DGM sinyallerinin üretilmesi için blok

şeması

Şekil 5: BASYS blok diyagramı.

Veri kayıtçısı bloğunda görev oranını belirleyen veri

saklanmaktadır. Ölü-zaman üreteci bloğunda DGM

sinyallerine eklenecek ölü-zaman üretilmektedir. Bu

çalışmada, DGM sinyallerinde görev oranı %50 olarak

ayarlandı ve ölü-zaman süresi için 8µs’lik bir gecikme

verilmiştir. Karşılaştırma bloğunda belirlenen görev oranı ve

verilen ölü zamana bağlı olarak DGM sinyalleri üretilir. Şekil

8’de FPGA ile üretilen iki kanallı DGM sinyalleri

görülmektedir. Burada ölü-zaman süresinin belirgin olması

açısından anahtarlama periyodu 6.10khz seçilmiştir.

103

A. Diker, Ö. F. Alçin, M. Gedikpınar

çalışmada, yük üzerindeki gerilimi sabit tutmak için çıkış

gerilim bilgisi analog sayısal dönüştürücü (ADC) ile 8-bitlik

veriye çevrilir. Bu 8-bitlik bilgi, veri kayıtçısına aktarılarak

DGM sinyallerinin görev oranı değiştirilir.

[1]

[2]

[3]

Şekil 8: Ölü zamanlı DGM sinyalleri.

FPGA yapılandırılması için donanım tanımlama

dillerinden (Hardware Description Language, HDL) VHDL

(Very-high-speed integrated circuits HDL) seçildi. Yazılan

VHDL programı kullanılan FPGA’nın üretici firmasının

Xilinx ISE paket programı kullanılarak derlenip FPGA’ya

yüklenmiştir. Üretilen DGM sinyalleri izolasyon devresi

kullanılarak yarım köprü evirici devresine uygulanmıştır. Yük

üzerindeki gerilim ve yükün akımı Şekil 9’da verilmiştir.

[4]

[5]

[6]

[7]

[8]

[9]

[10]

[11]

[12]

[13]

Şekil 9: Çıkış akım-gerilim grafikleri.

[14]

Şekil 9’daki osilaskop görüntüsünde 1 numaralı (Kanal 1)

sinyal yük üzerindeki gerilimi, 2 numaralı (Kanal 2) sinyal

yükün çektiği akımı göstermektedir. Yük akımının dalga

şeklinin osilaskopla görüntülenmesi için yüke seri 1Ω’luk

direnç kullanılmıştır.

V. SONUÇ

Bu çalışmada, FPGA ile DGM sinyalleri üretilmiş ve yarım

köprü eviriciye uygulanmıştır. FPGA kullanılarak DGM

sinyallerinin üretimi bir yonga ile gerçekleştirilmiştir. Böylece

donanım

maliyeti

azaltılmıştır.

FPGA’nın

yeniden

yapılandırılabilir yapısı istenilen değişikliğin yazılımda

yapılan değişiklikle elde edilmesine imkan sağlar. Bu özellik

ise yapılan çalışmaya esneklik kazandırmıştır. Yapılan

[15]

[16]

[17]

[18]

[19]

[20]

104

KAYNAKLAR

Z.Wenyi, C.Wensheng, ―Research on Voltage-Source PWM Inverter

Based on State Analysis Method‖, Proceedings of the 2009 IEEE

International Conference on Mechatronics and Automation August 9 12, Changchun, China, pp. 2183 – 2187.

M. Hiraki-Yoshida, E. Nakaoka, M, ―Comparative EMI evaluations of

three-phase ZVS-PWM and ZVZCS-PWM inverters‖, Power

Electronics and Drive Systems, 2003. PEDS 2003. The Fifth

International Conference on, vol.1, pp.108 – 113.

P. Karuppanan, K. Kanta Mahapatra, ―FPGA based cascaded multilevel

pulse width modulation for single phase inverter‖, Environment and

Electrical Engineering (EEEIC), 2010 9th International Conference on,

pp. 273 – 276.

P. Mal P.D. Patel, F.R. Beyette, ‖Design and Demonstration of a Fully

Integrated Multi-Technology FPGA: A Reconfigurable Architecture for

Photonic and Other Multi-Technology Applications‖, Circuits and

Systems I: Regular Papers, IEEE Transactions on, vol. 56, pp. 1182 –

1191, 2009.

S. Tagzout, K. Achour, O. Djekoune, ―Hough transform algorithm for

FPGA implementation‖, Signal Processing (81), 2001, pp. 1295-1301.

J. Shih-Liang, C. Meng-Yueh, J. Jin-Yi, H. Hsiang-Sung, Y. Li-Chia,

T.Ying-Yu, ―Design and implementation of an FPGA-based control IC

for the single-phase PWM inverter used in an UPS‖, Power Electronics

and Drive Systems, 1997. Proceedings., 1997 International Conference

on, vol.1, pp. 344 – 349.

L.Yong-Kai, L. Yen-Shin, ―Dead-Time Elimination Method and Current

Polarity Detection Circuit for Three-Phase PWM-Controlled Inverter‖,

Sustainable Energy Technologies, 2008. ICSET 2008. IEEE

International Conference on, pp. 130 – 135.

S.Kesler, ―Elektrik Makinaları Denetim Sistemlerinde TMS320F2812

DSP Kullanımı‖, AKADEMİK BİLİŞİM 2008.

E.Deniz, ―Beş Seviyeli İnverterlerin SDGM ile Kontrolü‖, Yüksek Lisans

Tezi, Fırat Üniversitesi Fen Bilimleri Enstitüsü, Elazığ, Ocak 2005.

W. Zhigan, Y. Jianping, ―A novel dead time compensation method for

PWM inverter‖, Power Electronics and Drive Systems, 2003. PEDS

2003. The Fifth International Conference on, vol.2, pp. 1258 – 1263.

H. Zhengyi, J. Xuewu, ―A new inverter compensation strategy based on

adjusting dead-time on-line ‖ Industrial Electronics, 2008. ISIE 2008.

IEEE International Symposium on, pp. 768 – 773.

J -R. Guoa, C. Youa, K. Zhoua, M. Chua, P. Currana, J. Diaoa, B.

Godab, R. Krafta, J. McDonalda, ―A 10GHz 4:1 MUX and 1:4

DEMUX implemented by a Gigahertz SiGe FPGA for fast ADC‖,

Integration, the VLSI Journal, Volume 38(3), 2005, pp. 525-540.

A.Doumar, H. Ito, ―FPGAs and Fault Tolerance‖,The 13th International

Conference on Microelectronics, pp. 222-225, Morocco, 2001.

M. Renovell, J. M. Portal, J. Figueras and Y. Zorian, ― Test Pattern and

Test Configuration Generation Methodology for the Logic of RAMBased FPGA‖, ATS'97, pp. 254-259.

I. Kuon, R. Tessier and J. Rose, ―FPGA Architecture: Survey and

Challenges‖, the essence of knowledge, Boston, 2008.

LK. Kumar, A. S. Ramani, A. J. Mupid, Kamkoti, V., ―Pseudo-online

testing methodologies for various components of field programmable

gate arrays‖, Microprocessors and Microsystems (29), 2005, pp. 99–

119.

İ.Şahin, İ. Koyuncu ―Grafik Sistemleri için FPGA Cihazlarında

Çalışmak üzere Tasarlanmış Matris Çarpım Motoru―, SAÜ. Fen

Bilimleri Dergisi, 12. Cilt, 1. Sayı, s. 61-68, 2008.

C.Fobel, G.Grewal, A.Morton, ―Hardware accrelerated FPGA

placemen‖, Microelectronics Journal (40), 2009, pp. 1667-1671.

J. S. Douglas,―Hdl chip design‖, Doone Publications, Madison, 1996.

(26,

December)

BASYS

Reference

Manuel,

Products/Detail.cfm?Prod=BASYS, http://www.digilentinc.com/